Semiconductors play a crucial role in our daily lives, as they are essential components of devices such as phones, computers, servers, and cars. With the gradual advancement of technology, the semiconductor manufacturing process has progressed from 10 microns (Intel 4004) in 1971 to 90 nanometers (Intel Pentium 4) in 2004, 7nm in 2019, 5nm in 2020, and 3nm in mass production this year, with even 2nm expected to enter mass production in 25 years. The leader in advanced processes has gradually shifted from Intel to TSMC. So, how much demand will there be for advanced processes in the future? This is the question we will attempt to answer in this article, written by BEDROCK member Jimmy and his team's discussion notes.

demand

Let's start by discussing demand. The most pressing demand for advanced processes comes from the mobile phone, computer, and server industries, which have a limited number of companies such as Apple, AMD, Nvidia, and others. Therefore, we can calculate the number of wafers each company needs based on the chip area.

Before we begin, let's clarify a few concepts:

Wafer: Refers specifically to silicon wafers in thin disk form. The commonly used sizes are 8 inches and 12 inches. In advanced processes, 12-inch wafers are mostly used, so this article assumes 12-inch wafers by default.

wafer die

Image Source:Wikipedia

Die: After the wafer undergoes processes such as lithography and etching, it becomes small pieces with the same circuit structure, called die. The small squares in the above image are die.

Gross Die Per Wafer (GDW): The maximum number of die that can be cut from a wafer. Because the parts near the edge cannot be used, the wafer area cannot be directly divided by the die area. Instead, an online calculator is used, such as the one trusted by Amkor and GF, or the following rough formula, which yields a larger estimate:

Die Per Wafer (free) Calculator - Trusted by Amkor and GF

Roughly speaking, you can also use the following formula directly, but the number of die calculated this way will be larger:

In the formula, d represents the diameter of the wafer and S represents the area of the die.

Good Die Per Wafer (GD): The maximum number of usable die that can be cut from a wafer. This concept involves yield rate, and generally, the total yield rate equals the wafer yield rate multiplied by the die yield rate multiplied by the packaging yield rate. To simplify the calculation, in this article, we only use the die yield rate, which can be assumed to include other yield rates as well.

Apple

Apple's demand for chips is divided into three parts:iPhone、iPad、Mac。

iPhone & iPad:

Since Apple releases new iPhone products in the fall every year, the annual sales of iPhones are actually composed of two generations of products. According to Omdia's data, we can see the approximate proportion of new and old products:

Image Source:Omdia

From this, we can predict the iPhone sales structure in 22 and 23:

Starting from 2022, Apple has adopted a new product strategy: only the Pro version of the new iPhone will use the new chip each year. Therefore, in 2022, only the Pro series of i14 will use the 4nm A16 chip, and in 2023, only the Pro series of i15 will use the 3nm A17 chip. Considering that the Pro series is more popular after the release of this year's new products, we assume that the sales ratio of the Pro series to the non-Pro series is 2:1.

In addition to sales, we also need to know the die area to calculate the wafer demand. We looked up the chip areas of Apple's previous generations of chips and found that when the process upgrade is significant, the die area will decrease, while when the process upgrade is relatively small, the die area will increase. Based on this, we assume that the 4nm A16 chip released in 2022 will increase in size by 20% compared to the A15, and the 3nm A17 chip released in 2023 will shrink in size by 10%. Assuming that the die shape is square, we can calculate the Gross Die Per Wafer using a calculator.

In addition, we also assume that the yield rate of 3nm is 75%, and the yield rates of 4nm and 5nm are 80%. Based on this, we can calculate the Good Die Per Wafer and the cost of each chip die based on the price of the wafer. Adding the packaging cost (about $3 per chip) gives the total cost of the chip, which is very close to the data from a major investment bank.

Based on the previously assumed sales of various iPhone models and iPad (which uses the A15 chip), we can calculate the number of 3nm, 4nm, 5nm, and 7nm wafers required for mobile phones and tablets each year, which adds up to about 600-800k wafers per year.

Mac:

Similarly, we can estimate the number of wafers needed for Mac. Since it is not clear whether the M2 Pro or M3 will be the first to adopt 3nm, we have made estimates for both scenarios, and the results show a difference of only about 10k 3nm wafers.

In summary, we have calculated that Apple will need 607k 5nm wafers and 65k 7nm wafers from TSMC in 2021, plus packaging and other types of chips. This accounts for approximately 20% of TSMC's revenue from Apple (actually 26%), with a margin of error of 6 percentage points, which may be due to factors such as yield, wafer prices, and the proportion of other chips.

In 2022, assuming that the price of 4nm wafers is the same as that of 5nm wafers, Apple's contribution to TSMC's revenue will decline slightly. In 2023, with Apple adopting the 3nm process, its revenue share is expected to increase again. Since the 3nm iPhone is expected to be sold only in the second half of 2023, we predict that Apple's revenue share will continue to rise until 2024.

AMD

In 2017, AMD launched the Ryzen series of processors, which marked the beginning of its journey to catch up with Intel. Recently, AMD released its latest desktop CPU product, the Ryzen 7000, which is the world's first computer CPU to adopt 5nm technology (manufactured by TSMC). Using a method similar to Apple, we estimated AMD's wafer demand and contribution to TSMC's revenue.

Unlike other companies, AMD uses Chiplet technology to divide a chip into several Chiplets, each using a different manufacturing process, thereby reducing chip manufacturing costs.

AMD mainly uses two types of Chiplets in its CPUs: the CPU core Chiplet and the I/O Die, which use different manufacturing processes. A CPU core Chiplet has eight cores, so depending on the CPU model, a CPU may contain one (up to 8 cores) or two CPU Chiplets (8 to 16 cores), and an I/O Die.

Source:Company Presentation

Zen 2 CPU Chiplet uses TSM 7nm process and has an area of about 72 mm²; its I/O Die uses GlobalFoundries 14nm process and has an area of 125 mm². Zen 3 CPU Chiplet uses TSM 7nm process and has an area of 83.736 mm²; its I/O Die uses TSM 12nm process and has an area of 124.29 mm². The latest released Zen 4 CPU Chiplet uses TSM 5nm process and has an area of 71 mm²; its I/O Die area has not been disclosed yet. Therefore, based on AMD's annual CPU shipment volume, we can estimate the required 5nm and 6nm wafer quantities. For server chips, we assume that their gross margin is the same as that of desktop CPUs, and therefore the required wafer quantity is proportional to the revenue scale.

At last, we calculate that AMD will need 298 thousand 5nm wafers and 337 thousand 6nm wafers in 2023, which corresponds to 9% of TSMC's revenue. Considering packaging costs and other businesses such as game console chips, this proportion is definitely underestimated.

Nvidia

Nvidia's GPU chip product line is slightly more complex, with die sizes varying by model: RTX20XX series, TSM 12nm, with 3 different die sizes from low-end to high-end: 445, 545, 754, with a median of 545. RTX30XX series, Samsung 8nm, with 4 different die sizes from low-end to high-end: 276, 393, 496, 628, with a median of 496. Based on GPU sales data, we can calculate a 5nm wafer demand of 568k for PCs in 2023. In 2022, PC GPU shipments will still be dominated by the 30XX series, which is manufactured by Samsung, so it will not contribute to TSMC's revenue. Datacenter GPUs have grown rapidly in recent years, and have been outsourced to TSMC since 2022. We found that the unit price of datacenter GPUs per unit area is much higher than that of gaming GPUs, so we assumed a 300% premium for datacenter GPUs. In 2022 and 2023, they will require 317k and 469k 5nm wafers, respectively. Overall, in 2022 Nvidia will only need 317k 5nm wafers from TSMC, which will grow to 1037k in 2023, mainly due to the shift of gaming GPU production from Samsung to TSMC. Nvidia's contribution to TSMC's revenue will also increase from 6% to 17%. It's worth noting that the die sizes we used may not necessarily reflect the average die size of GPU shipments, so the demand we calculated may be overestimated. Additionally, the release date for Nvidia's 40XX series GPU is still unknown and will need to be further monitored.

Intel

Unlike AMD and Nvidia, Intel operates on the IDM model, which means that both design and manufacturing are done in-house. However, it is expected that the 14th generation Core CPU (Meteor Lake), which will be released in 2023, will adopt a Chiplet design, and a part of the chips will be produced by TSMC. Previously, there were rumors that TSMC would manufacture the GPU part using the 3nm process. Considering the increase in transistor density brought by the 3nm process, we assumed that the GPU area accounts for 10% of the overall CPU chip, which would be 67k 12-inch wafers, accounting for 2% of TSMC's revenue. However, recently Intel announced that the GPU would use TSMC's 5nm, while the SOC would use TSMC's 6nm, with areas of around 20% and 40%, respectively. Based on this, we can calculate that Intel will contribute 6% of TSMC's revenue in 2023. Whether this can be achieved depends on whether the 14th generation Core CPU can be released in a timely manner.

Qualcomm

Qualcomm's previous flagship chip, Snapdragon 8 Gen 1, used Samsung's 4nm process, but suffered from severe heat generation. As a result, Qualcomm launched Snapdragon 8 Gen 1+ using TSMC's 4nm process, and is expected to continue using TSMC for the next generation of chips.

In 2021, global smartphone sales were 1.35 billion units, and Qualcomm's market share was 30%. Assuming half of them use advanced process technology, that would be 420,000 12-inch wafers, corresponding to 7% of TSMC's revenue.

MTK

MediaTek's chips are mainly focused on the low-end market, but in recent years, its Dimensity series chips have gradually entered the high-end market. In 2021, MediaTek's overall market share was 38% (based on sales), but assuming that its sales of high-end chips are only half of Qualcomm's, which is 8%, it corresponds to 199k 12-inch wafers, contributing 3% to TSMC's revenue.

Summary:

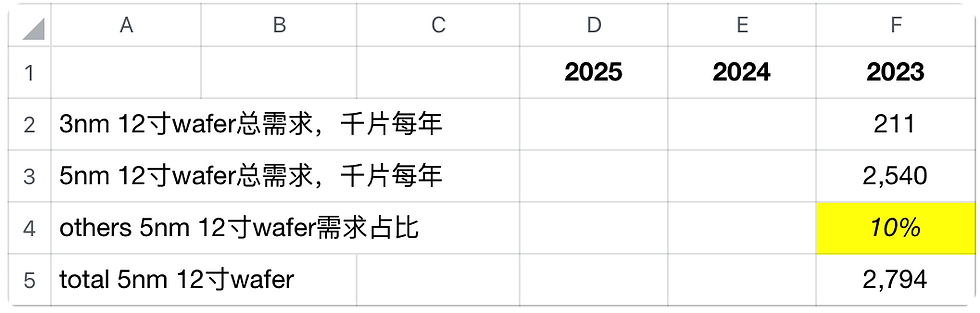

Adding up the demand of all the companies mentioned, we can get the demand for 3nm and 5nm wafers in 2023, which are 211k and 2540k respectively. Taking into account the demand for 5nm chips from other companies such as startups for autonomous driving chips and Arm server chips, the demand for 5nm wafers may increase by 10%, reaching 2794k wafers. Whether the supply can meet this demand will be calculated in the next article.

In summary, there are two main reasons driving the continuous increase in demand for advanced process semiconductor: the growth in chip size, at 10-20% annually, and the rising wafer prices resulting from process upgrades.

Finally, because much of the data is based on expert interviews or our own assumptions, there may be omissions or inaccuracies.

We welcome readers to point them out and engage in discussions with us.

Comments